随着芯片制程的发展和晶体管尺寸的持续微缩,传统硅基半导体器件达到了物理极限,面临着性能与功耗的瓶颈。以MoS2为代表的二维半导体材料,因其极限的物理厚度、表面原子级平整且无悬挂键、高本征迁移率、强的栅控能力,是解决当前晶体管微缩瓶颈,及构筑速度更快、功耗更低、亚10 nm 高性能半导体芯片的一类战略新材料。国际半导体联盟在2015年的技术路线图(International Technology Roadmap for Semiconductors, ITRS)中明确地指出二维半导体是下一代器件的关键材料。Intel在2021年也将基于二维MoS2的晶体管技术列为面向下一个十年的三大突破性技术之一。为了实现二维半导体全部潜力及其在高性能芯片上的应用,在商业通用衬底上可控合成出二维半导体单晶晶圆是非常必要的,但也极具挑战性。

针对二维半导体单晶晶圆的需求和制备挑战,国际上最领先的材料生长课题组都把这一问题作为重要课题进行攻关,目前已经在二维半导体单晶晶圆(如单层MoS2、WS2、WSe2)的制备上取得系列进展 [Nat. Nanotechnol. 16, 1201 (2021); Nat. Nanotechnol. 17, 33 (2022); Nat. Nanotechnol. 18, 1289 (2023)]。然而,目前二维半导体单晶晶圆制备主要依赖衬底台阶工程策略,这通常需要对基底进行特殊设计,如精心设计的斜切角或在苛刻的高温环境下进行退火处理等。与此同时,目前对二维半导体单晶晶圆的生长机理还存在很大争议。因此,如何实现在商业通用衬底上可控合成出二维半导体单晶晶圆,对深化理解生长机理和推动实际应用都至关重要。

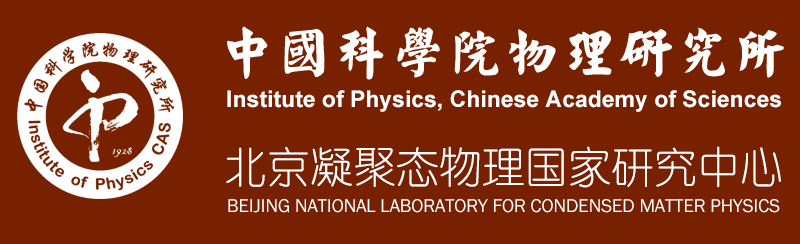

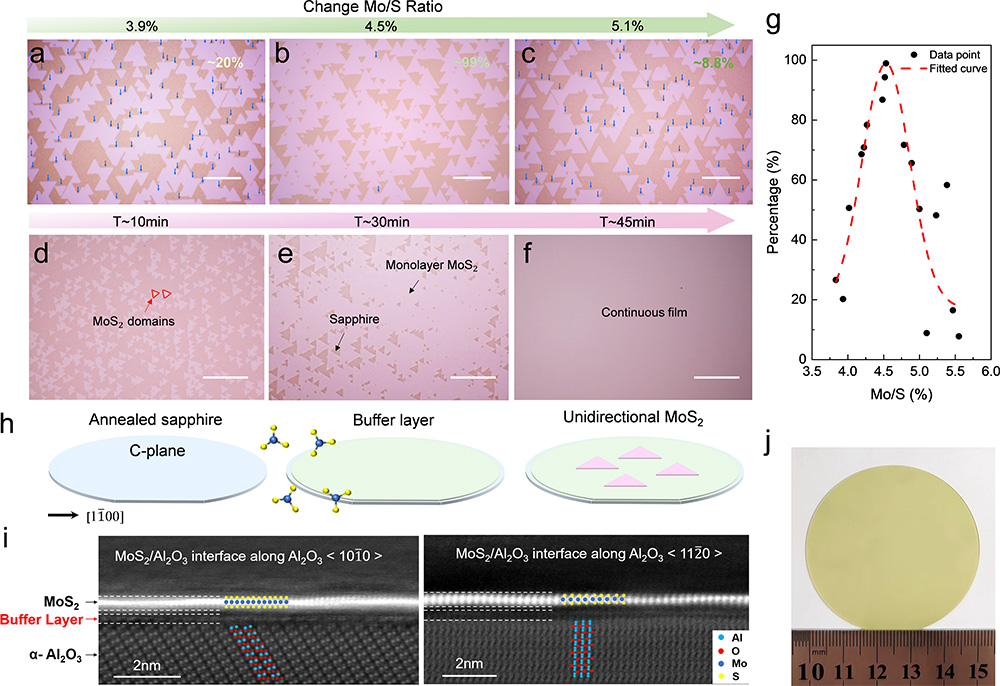

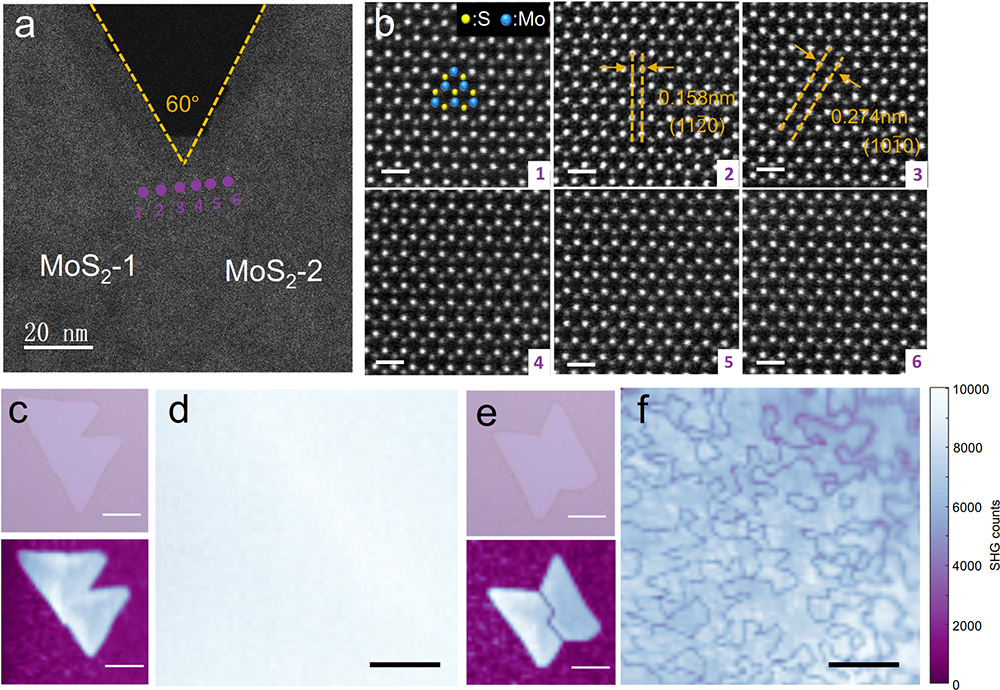

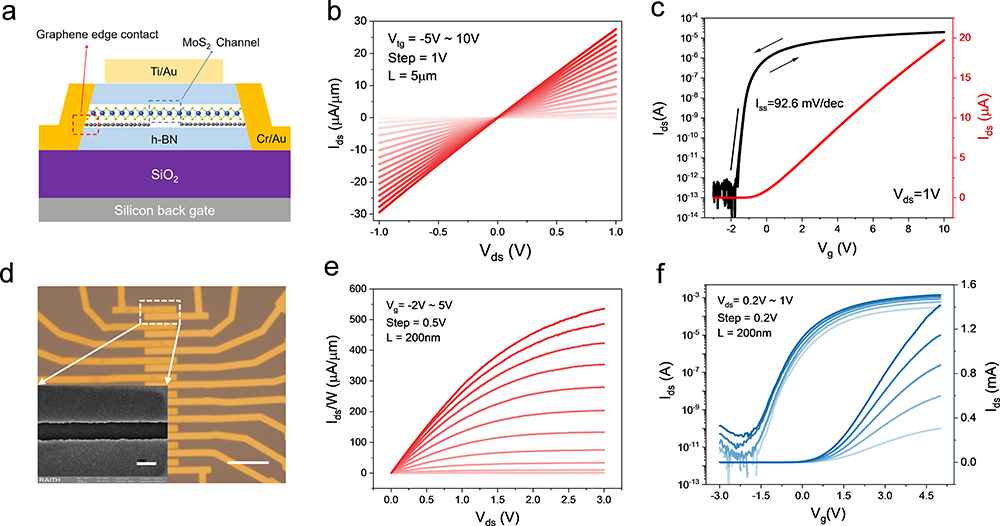

最近,中国科学院物理研究所/北京凝聚态物理国家研究中心N07课题组的李璐博士在杜罗军特聘研究员、张广宇研究员的指导下,基于前期在高质量二维MoS2晶圆外延生长方面的基础 [ACS Nano 11, 12001 (2017); Nano Lett. 20, 7193 (2020); Natl. Sci. Rev. 9, nwac077 (2022)],提出了一种界面缓冲层控制的新策略,通过精确控制前驱体的比例,调控生长动力学和界面缓冲层的形成,在工业兼容的 c面蓝宝石衬底上成功外延生长出 2 英寸单层MoS2单晶薄膜。通过从原子尺度到厘米尺度的跨尺度表征,充分证明了整个晶圆衬底上MoS2 晶粒的单一定向排列、晶粒间的无缝拼接、大面积均匀性。外延生长的单晶MoS2 单层具有优于以前生长的多晶甚至机械剥离单晶样品的超高质量,表现出超低的缺陷密度、完美的声子圆二色性、~70% 的优异激子谷极化特性、高的室温迁移率~140 cm2v-1s-1,以及接近109的开关比。相关研究成果以“Epitaxy of wafer-scale single-crystal MoS2 monolayer via buffer layer control”为题发表在Nature Communications 15, 1825 (2024)。

本工作为以MoS2为代表二维半导体单晶晶圆在商用绝缘体衬底上的外延制备提供了一种新策略,为基于二维半导体的大规模高性能电子学器件奠定了坚实的材料基础,预期可以有效地推动二维半导体材料在TFT、亚5 nm高性能芯片、柔性显示屏、智能可穿戴器件方面的应用。本研究工作获得来自中国科学院物理研究所白雪冬研究员、许杨特聘研究员、鲁年鹏特聘研究员、北京大学刘开辉教授、松山湖材料实验室冼乐德研究员、徐巧玲博士等的合作与支持。得到科技部重点研发计划,国家自然科学基金委,广东省重点研发计划,中国科学院先导B等项目的资助。

文章链接:https://www.nature.com/articles/s41467-024-46170-6

图1.通过缓冲层控制实现单层MoS2单晶晶圆的外延制备

图2. 单一定向排列晶粒间的无缝拼接

图3. 晶圆尺度均匀性和高的晶体质量

图4. 外延单晶薄膜优异的电学性能